导航

微信

顶部

发布时间:2026-04-24 阅读: 来源:管理员

EMI(Electromagnetic Interference,电磁干扰)是电子产品在工作过程中产生的电磁能量对自身或其他设备造成干扰的现象。

在实际项目中,超过70%的EMI问题源于PCB设计阶段(参考行业通用EMC设计经验,如IEC/CISPR相关标准设计指南)。一旦进入样机或量产阶段再整改,不仅成本高,还会影响交付周期。

换句话说:

EMI问题,本质是“设计问题”,不是“测试问题”。

1. 布局不合理(最常见)

典型问题:

- 数字电路与模拟电路混放

- 高速器件(CPU、DDR)靠近接口

- 电源模块靠近敏感信号

本质原因:

不同电路之间的“干扰路径”没有被隔离

2. 走线设计不规范

典型问题:

- 走线过长、形成大回路

- 差分对不等长、不对称

- 高速信号未控阻抗

影响:

- 增强辐射发射(RE)

- 信号反射导致EMI加剧

3. 接地设计不良(核心问题之一)

常见错误:

- 地平面被切割

- 回流路径不连续

- 模拟地/数字地处理错误

关键点:

信号走到哪里,回流就必须跟到哪里

4. 电源完整性不足(PI问题)

典型问题:

- 去耦电容位置不合理

- 电源纹波大

- PDN(电源分配网络)设计不完整

后果:

- 电源噪声耦合到信号

- 导致传导干扰(CE)超标

5. 高速/高频设计失控

随着产品向高速发展(如USB3.0、DDR、PCIe),EMI问题更突出:

- 阻抗不匹配

- 串扰(Crosstalk)

- 辐射增强

1. 合理分区布局(第一优先级)

- 模拟 / 数字 / 电源 / 射频分区

- 高速器件靠近连接器

- 噪声源远离敏感电路

原则:“源头隔离”优于后期整改

2. 控制回流路径(EMI设计核心)

- 保证完整地平面

- 高速信号下方必须有参考层

- 避免跨分割走线

3. 优化走线策略

- 高频信号走最短路径

- 差分对严格等长

- 控制阻抗(50Ω / 100Ω)

4. 加强电源去耦设计

- 多级去耦(0.1uF + 1uF + 10uF)

- 电容靠近电源引脚

- 使用低ESR电容

5. 屏蔽与滤波设计

- 接口增加EMI滤波器(如LC、π型)

- 外壳屏蔽设计

- 关键区域加地铜

6. 设计与打样协同优化(关键)

很多企业忽略这一点:

EMI不仅是设计问题,还与PCB制造工艺、叠层结构、材料选择强相关

例如:

- 叠层结构不合理 → 回流路径异常

- 板材介电常数不稳定 → 阻抗失控

- 加工误差 → EMI偏差

为了真正降低EMI风险,建议采用“一体化策略”:

1. PCB设计阶段

- 引入EMC设计规范(如CISPR/IEC设计指南)

- 进行SI/PI仿真

2. PCB打样阶段

- 控制阻抗一致性

- 验证叠层结构

3. PCBA阶段

- 关键器件选型(低噪声)

- 焊接质量控制(避免寄生效应)

4. 测试阶段

- 预扫描(Pre-scan)

- 快速定位EMI源

核心原因只有一个:

没有在PCB设计阶段解决问题,而是在测试阶段“被动修补”

常见后果:

- 反复改板(2~5次)

- 延误项目周期

- 成本增加30%以上

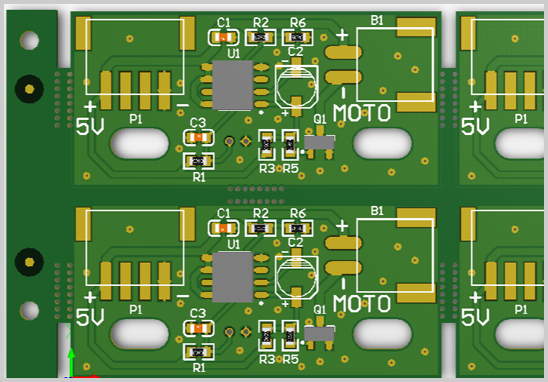

作为专业PCB设计及PCBA一站式服务商,深圳宏力捷电子可为客户提供从“原理图 → 量产交付”的全流程支持,重点解决EMI及产品可靠性问题:

1. PCB设计能力

- 多层板(4~20层)高精密设计

- BGA封装、高速信号(DDR/USB/PCIe)设计

- 盲孔/埋孔/HDI复杂结构设计

- EMC/EMI优化设计经验丰富

2. PCB打样与制造

- 高速阻抗控制

- 多种板材(FR4、高频板等)

- 快速打样(缩短研发周期)

3. PCBA代工代料(OEM/ODM)

- BOM整理与优化

- 元器件采购(优质供应链)

- SMT/DIP生产

- 小批量试产到大批量交付

4. EMI问题专项支持

- 设计阶段EMI预防

- 打样阶段问题定位

- 协助EMC整改与测试通过

如果你的产品正面临:

- EMI测试不过

- 高速PCB设计难度大

- 打样周期长、反复改板

本质问题往往出在设计+制造脱节。

选择具备“PCB设计 + 打样 + PCBA代工代料”一体化能力的团队,可以从源头降低EMI风险,提升一次成功率。

如需评估项目或优化现有设计方案,欢迎沟通具体需求,我们可提供针对性的工程建议与落地支持。

获取报价